AI Datacenters are Reshaping the Optics Industry

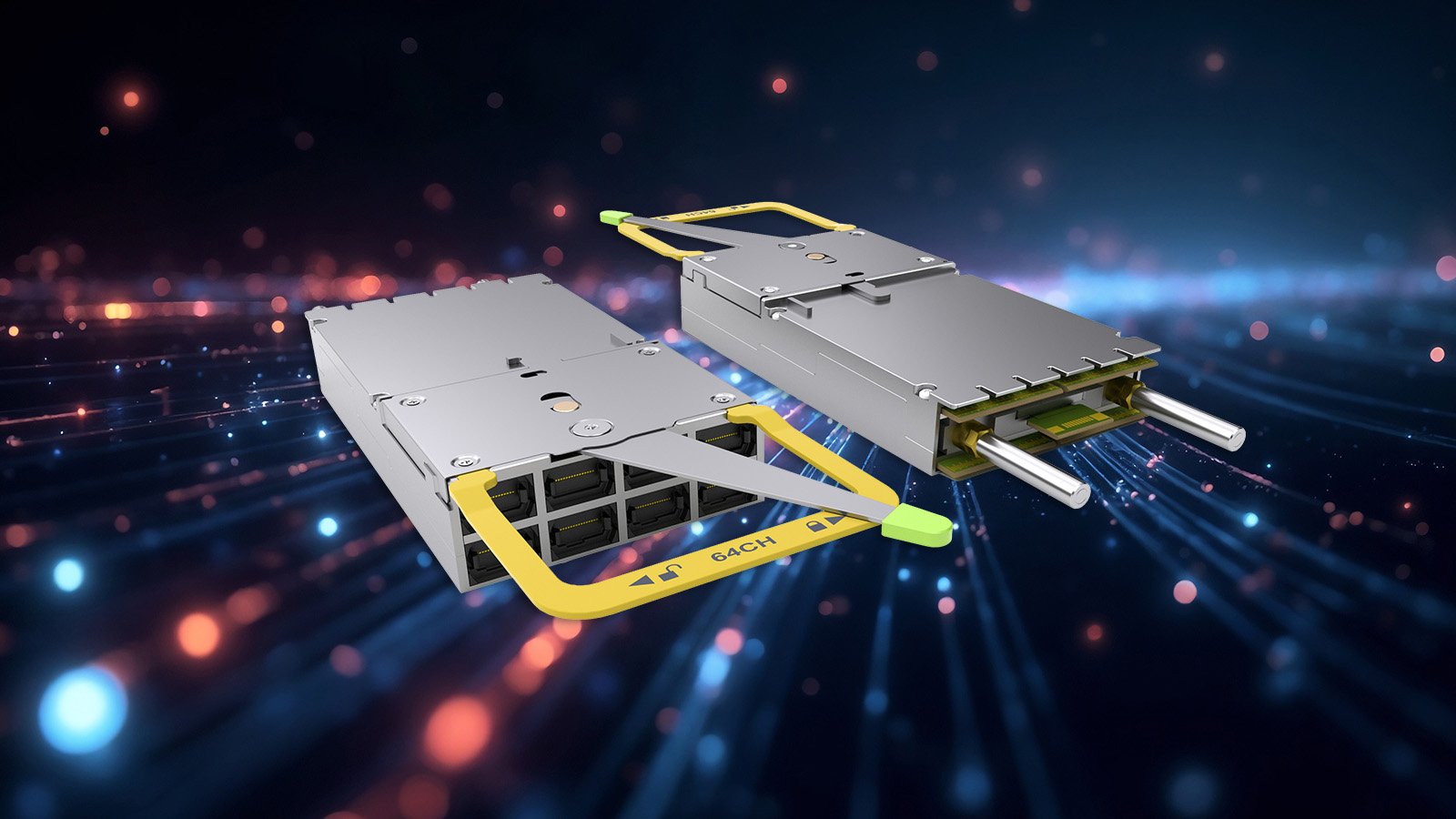

In 2016, Arista Networks together with powerful industry leaders, announced the OSFP (Octal Small Form-Factor Pluggable) specification and...

These days there is much discussion whether switches or routers should be built with proprietary custom ASICs or standard "merchant silicon" chips. At one level, the question is "Why does it matter?" After all, networking vendors have been building custom silicon chips since the invention of the LAN switch in the early '90s.

In my own career, I have led the development of several generations of very high volume network switch silicon. However, even I could not design better silicon switch chips than what is available now on the merchant market. To me this is an inflection point for the industry that is not unlike what happened in the computer industry with the adoption of industry standard architectures.

While CPU and switch silicon architectures differ in many ways, the underlying economics are very similar. In the 1980s and 1990s, CPU architectures flourished: there were MIPS, PowerPC, SPARC, ARM, and X86. Each architecture staked out their position in the market. The RISC architectures led the server market with 64-bit addressing and multi-processing capability, and also focussed on embedded applications. X86 was the standard for desktop computers. However as the years passed, most of the volume growth in the market has accrued to the industry standard X86 architecture, which now dominates the server architectures as well. It may not have had all the capabilities of RISC but it delivered the best cost-performance.

We are now starting to witness the same transition in the design of network switches. While the majority of switches are still built based on custom silicon designs, we are at a fork in the road where the vertically integrated approach will transition to using merchant silicon. It will take a while for this to play out, but the outcome is inevitable. The history of silicon technology has demonstrated that, over the long term, economics always wins.

Let us first examine why in-house switch ASICs were built. In the early 1990's, the beginning of network switches, there were no merchant silicon choices that provided the functionality or the throughput needed. As a result, a large number of startup companies emerged, each designing their own switching chips using the low-cost ASIC technology available at the time. It also allowed vendors to add proprietary features to their switch silicon in an attempt to achieve customer lock-in.

While this model became the accepted business model for the $16B LAN switching market, a number of problems emerged with this approach over the last several years.

First, the inevitable march of silicon technology to finer and finer geometries has greatly increased the cost of doing custom switch chips. Where a switch chip in the '90s could be built for hundred thousands of dollars, the cost of doing a full custom chip today is tens of millions. This completely changed the economics of doing custom silicon design.

Second, switch architecture has stabilized to the point where it is no longer possible to drive significant feature differentiation at the silicon level. As a result, there is little advantage to be gained with proprietary switch chips.

And last but not the least, customers are not desiring to get locked into proprietary switch silicon features and have become keenly aware of the cost of proprietary switch architectures, especially in the current economy.

Fortunately, by now enterprise switch architecture has matured to the point where its requirements can be fully addressed with the latest generation of merchant switch silicon, doing away with the need to develop custom chips. This benefits customers because products based on merchant silicon have significantly better cost-performance than switch products designed with proprietary ASICs.

There are at least five silicon companies developing compelling silicon for LAN network switches. All of these vendors are building standards compliant components, with high caliber engineering teams targeting the latest silicon processes with highly optimized design flows, which results in smaller die sizes and lower power consumption than what can be achieved with ASIC flows. Vendors are taking innovative approaches with programmable data plane functions and high density on-chip memories designs. There is an intense competition between silicon vendors to provide the highest switch chip performance and functionality. Due to this vibrant competition, innovation is now happening faster in merchant silicon than with traditional proprietary in-house switch silicon.

At Arista, we started by writing the next generation of switching software, our EOS (Extensible Operating System), long before we even picked a switch silicon architecture. This allowed us to focus on building the most robust software architecture in the industry, while giving us the choice to use the best merchant silicon switch architectures available.

We are proud to have partnered with leading merchant silicon vendors to deliver best-of-breed switching products that offer the lowest latency, the highest density and the best cost-performance in the market today. We have sold these products to a large number of customers in the web, financial, technical, and high-performance computing markets that all appreciated the performance advantages.

And we have achieved all of this without spending a dollar on custom chip development. Yes, times have changed. Welcome to the new world of cloud networking and 10 GigE switching for the next decade!

Comments are welcome: feedback@arista.com

In 2016, Arista Networks together with powerful industry leaders, announced the OSFP (Octal Small Form-Factor Pluggable) specification and...

Leaf-spine architectures have been widely deployed in the cloud, a model pioneered and popularized by Arista since 2008. Arista’s flagship 7800...

The explosive growth of generative AI and the demands of massive-scale cloud architectures have fundamentally redefined data center networking...